Table of Contents

Not every update needs to be flashy. Sometimes the best improvements are the ones that make everything else work more smoothly. This revision focuses on the infrastructure that keeps NeoCore running reliably and makes development life considerably less painful.

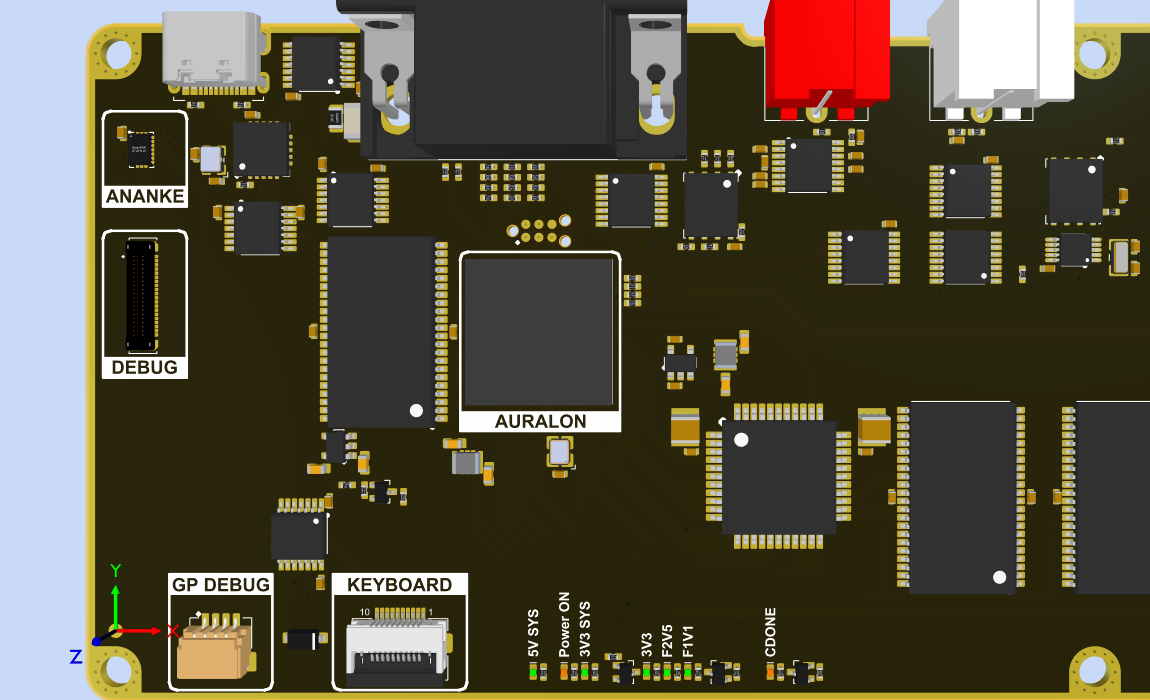

Housekeeping Gets a new brain

The change is a new GreenPAK IC handling what we're calling "housekeeping", all the unglamorous but essential functions that a robust system needs. Reset sequencing, a hardware watchdog, power-on from keyboard, and support for both the debug interface and on-board development push buttons are now managed by this single, tidy little chip. It keeps the FPGA out of the business of babysitting itself, which is exactly how it should be.

A Proper Debug Connector

I have added a dedicated connector for our JTAG/UART/GPIO/Rails debugger — a compact unit with its own display that can program chips over JTAG, provides two debug UARTs, 16 general-purpose I/O pins, and can monitor up to 8 voltage rails simultaneously. No more juggling adapters and flying wires during development. Plug in, power up, and you've got full visibility into what the hardware is doing.

SPI Programming Interface Reworked

The SPI bus used for programming internal memories and the RTC has been updated for cleaner access. All on-board memories are now reachable through a single, consistent interface.

EEPROM Removed

I have dropped the EEPROM from the design. The battery-backed RAM provides everything we need for persistent configuration and settings storage, and removing the EEPROM simplifies both the board layout and the software stack. One less chip, one less thing to go wrong.