Table of Contents

Background

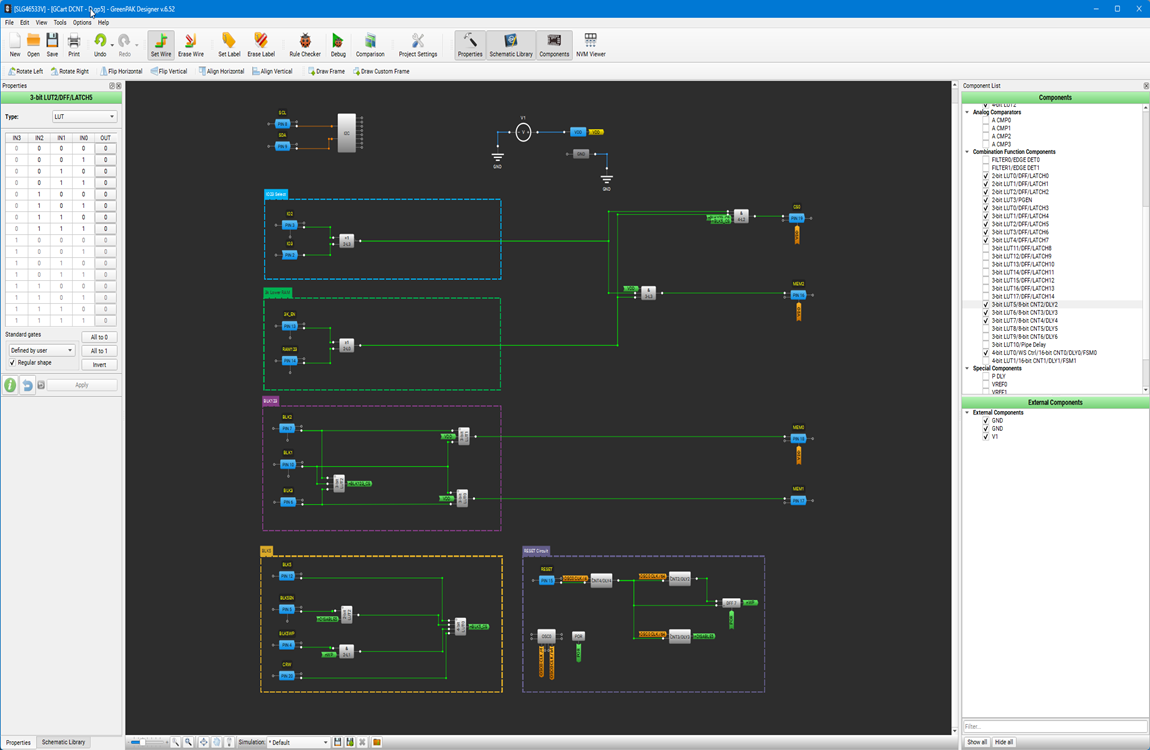

GCart DCNT has, for all intents and purposes, only 2 active components. First the actuall memory which is a 128k SRAM. Then a programmable logic/analog circuit from GreenPAK. These are one of my absolute favorites. I have been using them for a decade now, but on every new assignment I come (as a electronic consultant) they are news.

Anyway.

What is it?

Green PAK is a series of programmable logic/analog chips. They are OTP - One Time Programmable, so it needs to be free of bugs. They have a large selection of building blocks, such as; Gates, Delay lines, Counters, I2C,/SPI, Edge detectors, Flip-flops. I also have 2 oscillators. Some have Pattern Generators, Operational Amplifiers/Comparators, Rheostats, and State Machines.

And it works with 5V which suits us "retro tinkers" very well.

In GCart DCNT there is a SLG46533V which is a mid-range of the available types.

What does it do in GCart DCNT?

- Decodes BLK1,2,3 and 5 with IO2 and 3 as well as RAM1,2 and3 into CS for the SRAM as well as the upper 3 bits for selecting correct 8k bank.

- Decodes BLK1,2,3 and 5 with IO2 and 3 as well as RAM1,2 and3 into 3 bits A13-A15. Each block is 8k and IO2, 3 and RAM1, 2 and 3 occupies one 8k block.

- Manages BLK5 write protection, by gating the BLK5 to CS.

- Deglitches and Monitors the RESET signal for short press (<0.5s), long press (0.5s to 1s) and extended (>1s) press. These in turn enables temporary write protection and temporary disable of BLK5.

Implementation

The decoding is pretty straight forward and not much to write hoem about. If you have not heard about GreenPAK, then perhaps the reset monitoring can be interrsting though.

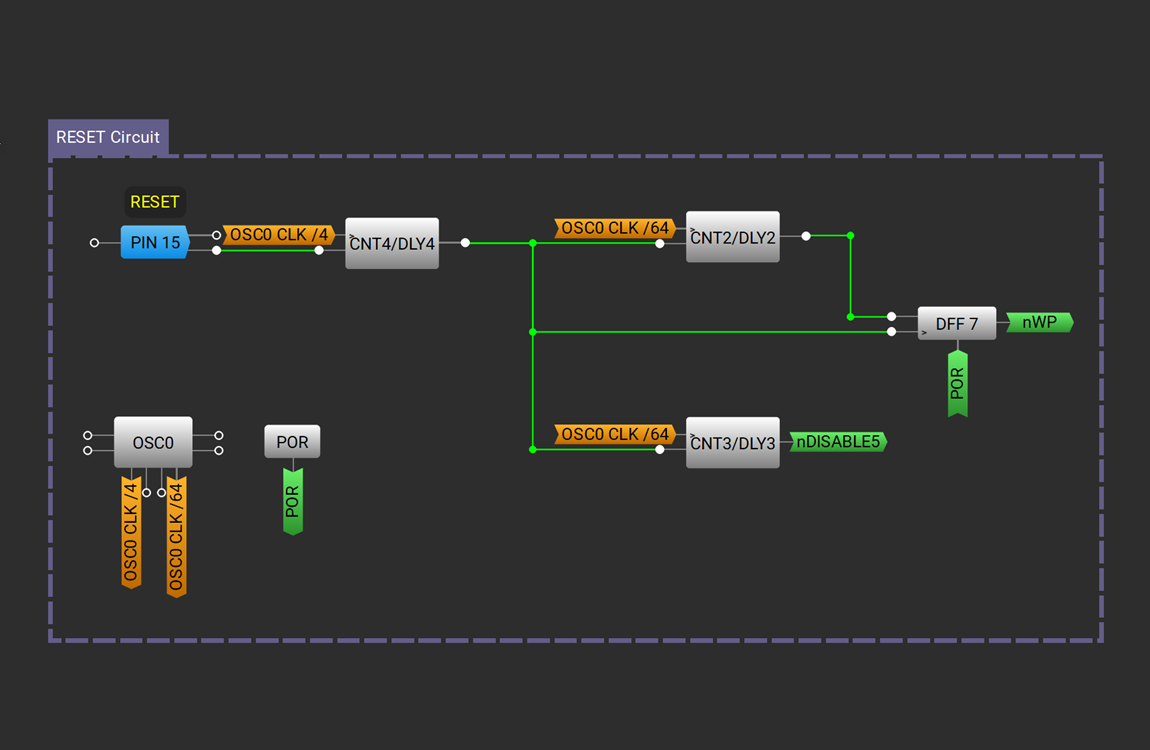

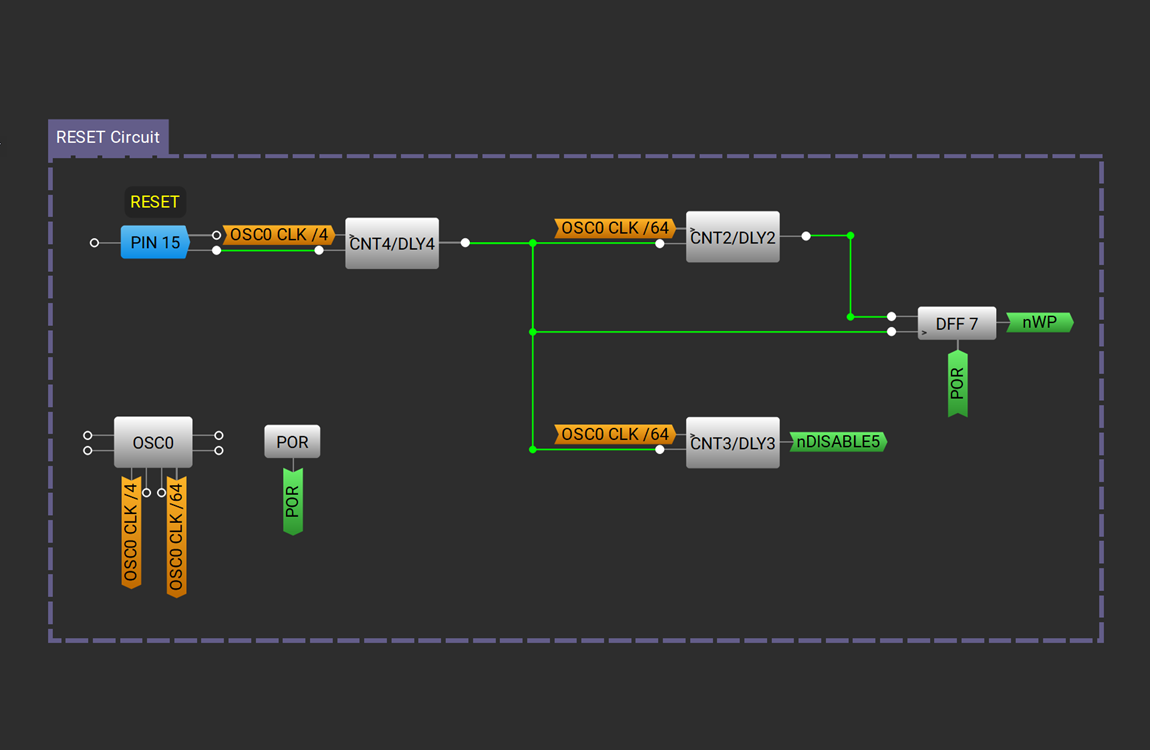

RESET Circuit

The POR is a Power on Reset. It ios driven low during start-up and makes sure the Flip-Flop DFF7 is at a reset state at power on.

OSC0 is the oscillator for the delay lines. It is configured as a 25kHz RC oscillator. It has 2 outputs. One divided by 4 and one divided by 64.

CNT4/DLY4 is configured as a delay of ~50ms. It is triggered on both rising and faling edges. Any change on the input needs to be stable for ~50ms to follow through. This is a deglitch filter. After that we have very clean reset singlas no matter where they come from on the VIC20.

This deglitched RESET is feed into two additional delay blocks CNT2/DLY2 and CNT3/DLY3. They are also triggered on both rising and faling edges. The CNT2/DLY2 has a delay of 500ms and the CNT3/DLY3 has 1s.

So a long press will follow through on CNT2/DLY2 after 500ms and CNT3/DLY3 after 1s.

When RESET is released, it's rising edge will lock the CNT2/DLY2 value in DFF7. This in turn will write protect, or not, BLK5. Regardless of what the DUP switch is set to.

If the reset was a extended press, then nDISABLE5 is activated. This temporarily disables BLK5. After another second after RESET goes high, CBT3/DLY3 also goes high and BLK5 is enabled again. But during that time the Kernal has missed any cartridge image in BLK5 and skipped it, exiting top BASIC.

For a short press neither CNT2/DLY3 nor CNR3/DLY3 will engage.